# Digital Technical Journal

digital

PARALLEL SCSI TECHNOLOGY ROUTER CLUSTERS MULTIPLATFORM 3-D APPLICATION SHARING

HPF DEBUGGER

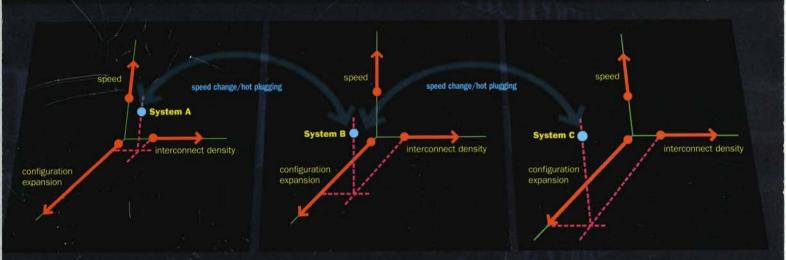

speed change/hot plugging

onfiguration expansion

speed change/hot plugging

configuration expansion

onfiguration expansion

UltraSCSI UltraSCSI UltraSCSI UltraSCSI UltraSCSI UltraSCSI UltraSCSI UltraSCSI

Volume 9 Number 3 1997

#### Editorial

Jane C. Blake, Managing Editor Kathleen M. Stetson, Editor Helen L. Patterson, Editor

#### Circulation

Catherine M. Phillips, Manager Kristine M. Lowe, Administrator

#### Production

Christa W. Jessico, Production Editor Elizabeth McGrail, Typographer Peter R. Woodbury, Illustrator

#### Advisory Board

Samuel H. Fuller, Chairman Scott E. Cutler Thomas F. Gannon Donald Z. Harbert William A. Laing Richard F. Lary Alan G. Nemeth Robert M. Supnik

#### Cover Design

Recent advances in physical technology have significantly improved the capabilities of parallel SCSI in three parameters: speed, interconnect density, and configuration expansion (device count, length, topology, control). On the cover, the graphs represent three systems with different sets of parameter values, that is, three unique points in the speed-size-configuration space. Hot plugging of devices and bus segments and dynamic speed changes can decrease or increase the parameter values without system disruption. The opening paper in this issue describes these advances in parallel SCSI technology.

The cover design is by Lucinda O'Neill of the DIGITAL Industrial and Graphic Design Group. The editors thank author Bill Ham for his help in developing the cover concept. The Digital Technical Journal is a refereed journal published quarterly by Digital Equipment Corporation, 50 Nagog Park, AKO2-3/B3, Acton, MA 01720-9843.

Hard-copy subscriptions can be ordered by sending a check in U.S. funds (made payable to Digital Equipment Corporation) to the published-by address. General subscription rates are \$40,00 (non-U.S. \$60) for four issues and \$75.00 (non-U.S. \$115) for eight issues. University and college professors and Ph.D. students in the electrical engineering and computer science fields teceive complimentary subscriptions upon request. DIGITAL customers may qualify for gift subscriptions and are encouraged to contact their account representatives.

Electronic subscriptions are available at no charge by accessing URL http://www.digital.com/info/subscription. This service will send an electronic mail notification when a new issue is available on the Internet.

Single copies and back issues can be ordered by sending the requested issue's volume and number and a check for \$16.00 (non-U.S. \$18) each to the published-by address. Recent issues are also available on the Internet at http://www.digital.com/info/dtj.

DIGITAL employees may order subscriptions through Readers Choice at URL http://webrc.das.dec.com.

Inquiries, address changes, and complimentary subscription orders can be sent to the *Digital Technical Journal* at the published-by address or the electronic mail address, **dtj@digital.com**. Inquiries can also be made by calling the *Journal* office at 978-264-7556.

Comments on the content of any paper and requests to contact authors are welcomed and may be sent to the managing editor at the published-by or electronic mail address.

Copyright © 1998 Digital Equipment Corporation. Copying without fee is permitted provided that such copies are made for use in educational institutions by faculty members and are not distributed for commercial advantage. Abstracting with credit of Digital Equipment Corporation's authorship is permitted.

The information in the *Journal* is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation or by the companies herein represented. Digital Equipment Corporation assumes no responsibility for any errors that may appear in the *Journal*.

#### ISSN 0898-901X

Documentation Number EC-P8826-20

Book production was done by Quantic Communications, Inc.

The following are trademarks of Digital Equipment Corporation: AlphaServer, AlphaStation, CI, DECnet, DECNIS, DIGITAL, the DIGITAL logo, DIGITAL UNIX, and PowerStorm.

Betamax is a trademark of Sony Corporation.

CRAY is a registered trademark of Cray Research, Inc.

Direct3D is a trademark of 3Dlabs, Inc. Ltd.

Microsoft, Visual C++, Windows, Windows 95, and Windows NT are registered trademarks and NetMeeting is a trademark of Microsoft Corporation.

Netscape Communicator is a trademark of Netscape Communications Corporation.

Pro/ENGINEER is a registered trademark of Parametric Technology Corporation.

TotalView is a trademark of Dolphin Interconnect Systems, Inc.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Ltd.

WinFrame is a registered trademark of Citrix Systems, Inc.

## Contents

| Foreword                                                                                                                   | Richard Lary                            | 3  |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----|

| Recent Advances in Basic Physical Technology for<br>Parallel SCSI: UltraSCSI, Expanders, Interconnect,<br>and Hot Plugging | William E. Ham                          | 6  |

| Development of Router Clusters to Provide Fast Failover<br>in IP Networks                                                  | Peter L. Higginson and Michael C. Shand | 32 |

| Shared Desktop: A Collaborative Tool for Sharing 3-D<br>Applications among Different Window Systems                        | Lawrence G. Palmer and Ricky S. Palmer  | 42 |

| Challenges in Designing an HPF Debugger                                                                                    | David C. P. LaFrance-Linden             | 50 |

## Editor's Introduction

This issue of the *Digital Technical Journal* presents papers on a range of computing subjects, beginning with recent advances in storage technologies, followed by network router cluster enhancements, new desktop software for sharing 3-D applications across platforms, and an experimental High Performance Fortran debugger.

DIGITAL's storage engineers have been leaders in the definition of the parallel small computer system interface (SCSI) ANSI standards and in related technology improvements. Bill Ham's paper focuses on four advances in the physical features of SCSI that resulted in major increases in SCSI capabilities and minor disturbances when incorporated in existing installations. The discussion spans developments from SCSI-2 through UltraSCSI, including speed increases in the synchronous data phase; longer, more complex configurations enabled by bus expanders; physical versatility inherent in a decreased size of the interconnect; and dynamic removal and replacement of devices on an active bus (hot plugging).

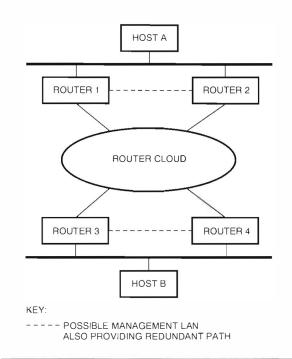

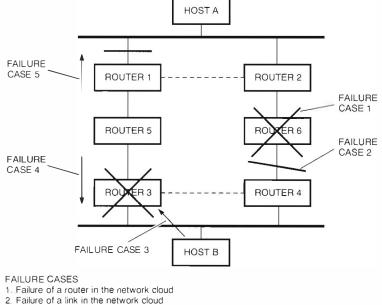

The subject of our next paper is networks, and the emphasis of the engineering is on customer requirements for reliability and availability. Router clusters, described here by Peter Higginson and Mike Shand, were developed to provide fast failover response in IP networks and are defined as a group of routers on the same local area network (LAN) providing mutual backup. New router cluster protocols and mechanisms restrict the loss of service that results from a failure on the network, specifically on networks requiring high availability, such as telecommunication and stock exchange networks. The authors analyze failure cases and present the solutions that reduced service-loss time from approximately 30 to 45 seconds to 5 seconds in both LAN and WAN environments.

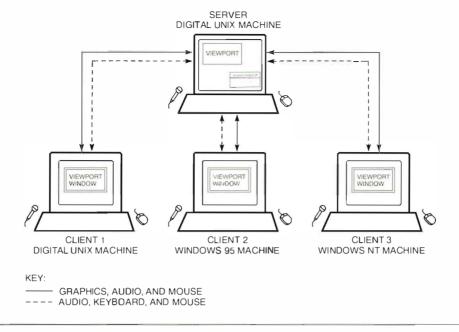

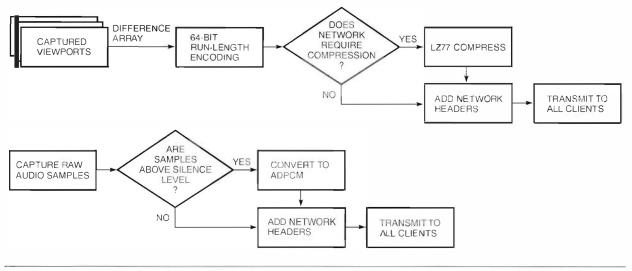

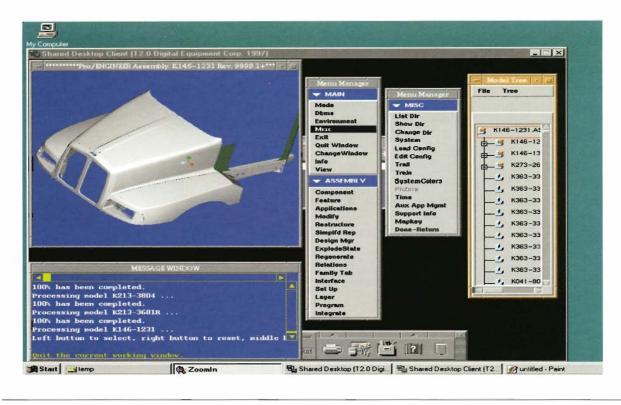

Collaboration software for desktop systems can be broadly defined to encompass a range of capabilities, from a simple transfer of data between users, such as e-mail sent over a network, to real-time sharing of text, graphics, and audio and video data. Larry and Ricky Palmer have designed a software product, called Shared Desktop, for users who want to share three-dimensional graphics applications and audio across networks. Notably, the design differentiates itself by supporting multiple operating systems, currently enabling realtime interoperation among Windows and UNIX systems. The authors discuss the decision to create a "viewport," which is a part of the desktop screen, and issues they addressed during implementation, including protocol splitting, screen capture and data handling, and dissimilar frame buffers. They conclude with ideas for possible enhancement of the product in the future

In a previous issue of the *Journal* featuring technical computing topics (vol. 7 no. 3), Jonathan Harris et al. described DIGITAL's Fortran 90 compiler that implements High Performance Fortran version 1.1, a language for writing parallel programs. An outgrowth of that work is an experimental debugger, code-

named Aardvark, that "reconstructs" for the HPF programmer a single source-level view, even though the program has several flows of control and the data are distributed. David LaFrance-Linden discusses the challenges faced in creating the debugger and describes useful techniques and concepts, such as logical entities, that can be generally applied to debugger design.

Readers interested in past issues of the *Journal* are invited to visit the *Journal* Web site at http://www. digital.com/info/dtj/. Our next issue will address such topics as optimization of NT executables on Alpha, a new graphics program, and VLM. A Special Issue on programming languages and tools is being developed for publication in the fall of 1998.

ane Blake

Jane C. Blake Managing Editor

### Foreword

Richard Lary DIGITAL Storage Technical Director

Welcome to the winter 1997-98 issue of the *Digital Technical Journal*. This issue does not have a single theme; it contains a potpourri of papers on a wide range of technical topics. This provides the foreword writer with a small gift and a not-so-small headache.

The gift is the opportunity to tout the continuing fecundity of DIGITAL's engineering community. All the papers in this issue of the Journal come from product development groupsin DIGITAL, and all the technology described herein is directly applicable to the problems of using computers in the real world. The papers themselves cover a wide range of topics: designing storage buses and their infrastructure; building IP routers that reduce network delays caused by link or router failure; sharing 3-D graphical and audio data across networks of computers with different windowing systems; and debugging programs written in languages that incorporate data parallelism.

The headache, of course, stems from this very diversity. Any attempt to derive some set of common underlying principles other than "make better stuff" from this collection is doomed to sophistry. And my technical background is too narrow to provide any significant embellishment to any of the papers outside the domain of storage systems. So, with apologies to the other authors, I am forced to restrict my comments to what I know -the background and impact of Bill Ham's work on advances in parallel SCSI which are presented in his paper in this Journal.

Bill Ham's paper not only describes a significant technical achievement; it illustrates DIGITAL's shift from engineering proprietary storage systems to engineering open storage systems.

The SCSI bus was developed during the early 1980s as one of many attempts to standardize the interface to storage devices. It succeeded beyond the expectations of its developers, largely because it supported a device model that was abstract enough to be extensible but inexpensive enough to be implemented in the technology of the time. For all its advantages, however, SCSI suffered from poor engineering at the physical level. This was a direct result of the way it was developed. The diverse corporate representatives that defined SCSI did not have the time or money to specify and build custom bus infrastructure components (transceivers, cables, terminators, etc.), so they used commonly available parts. A lack of sophistication in specifying physical interface parameters resulted in a specification that allowed too much component variation. As a result, it was difficult to build reliable, multi-box systems using SCSI.

DIGITAL's attitude towards SCSI during this period was to ignore it and hope it would go away. We had designed our own proprietary Digital Storage Architecture (DSA), which utilized an abstract and extensible device model and also incorporated many large system features, including a robust physical interconnect. We controlled the design and manufacture of all DSA components and could thus guarantee that they all met tight architectural specifications. Moreover, DSA was a key enabling technology for VMS Clusters, the individual DSA components were competitive with their counterparts

from the proprietary storage architectures of other large systems companies, our customers were happy, and the storage business was profitable. We were feeling quite pleased with ourselves—and we were profoundly ignorant of the power of a successful open market standard, since one had never existed in the storage world.

During the latter half of the 1980s, SCSI grew steadily in popularity until it dominated the workstation and small-server markets. These systems had at most a few disk drives on them, and SCSI's signal integrity problems were manageable in that context. They were not manageable in the larger and more demanding data center systems, and so SCSI was not used there. The SCSI standards group was aware of the bus's deficiencies, however, and as the decade progressed, the group made amendments to the standard to eliminate many of them. By the turn of the decade, several independent subsystem vendors were selling subsystems utilizing SCSI devices as storage for large DIGITAL systems. These subsystems did not, in general, have the features, performance, or robustness of our subsystems, but they were significantly cheaper and improving all the time. By 1991, it had become obvious to us that we would not be able to compete with these systems in the long run. They were leveraging an entire industry's investment and talent and were reaping the cost benefits of high-volume manufacturing; whereas we had to design and manufacture (at relatively low volume) every component of every DSA system ourselves.

Our position was untenable. We had to change our strategy and embrace the bus that we had so studiously ignored.

We designed a modular packaging architecture for SCSI devices (known commercially as StorageWorks) and a set of storage array controllers that interfaced these devices to our systems (and systems from other major vendors as well). We also became active participants in the SCSI standards process. Where DIGITAL had previously sent one or two engineers to SCSI standards meetings strictly to gather information, we started to send up to half-a-dozen engineers to listen, learn, participate in debate, help with the grunt work of the standards process, and make proposals to amend or extend the standard in directions useful to us and our customers.

Our new modular packaging design allowed our customers to install and remove storage devices themselves and to migrate storage devices between systems, even between systems built by different system vendors. This modularity proved to be a very valuable feature to our customers. However, it required us to build a physical infrastructure for the SCSI bus that had the robustness needed by our large systems and that could accommodate a great deal of variability in configuration, and to use a bus that was known to have residual signal integrity problems in its physical interconnect. We were understandably worried about this, worried enough to charter a small group of engineers as a SCSI Bus Technical Office (SBTO) within the storage group, and to develop

short-term configuration guidelines for our packaging architecture and long-term technical proposals for the SCSI physical bus architecture. Bill Ham has been the head of SBTO since its inception and has also been our representative to the SCSI committee on all matters relating to the physical bus interconnect.

In the summer of 1993, Bill completed a study of the signal integrity issues surrounding parallel SCSI. His conclusions were startling. The SCSI standards committee had, over the years, made enough improvements in the basic transmission line characteristics of the SCSI bus that most of the remaining signal integrity problems were due to the variations in component parameters allowed by the SCSI specification. Exercising tighter control over component variationthrough building selected components or through purchase specifications with our suppliers-would not only produce excellent signal integrity in our packaging but would allow the maximum clock rate of the bus to be doubled while maintaining excellent signal integrity and backwards compatibility with existing SCSI devices. Bill's results also indicated that the maximum clock rate could be increased even further, with more work.

This discovery came at a critical time in the evolution of the SCSI standard. Much of the SCSI standard committee's effort in the early part of the 1990s was being spent in modifying the SCSI standard so that serial buses could carry the higher level SCSI bus protocols. The committee had started this work under the assumption that parallel SCSI was "out of gas" in performance, and the new serial bus variants would supplant it by mid-decade. However, by 1993 not only was the definition and implementation of the serial bus going slower than expected, but there were three independent and incompatible serial bus proposals, each with unique useful features and unique drawbacks, each with a cadre of supporters among the industry representatives. The market would ultimately choose which serial buses would thrive; but it was highly unlikely that all three would thrive. Storage vendors that made the wrong bus choice would suffer for it. Most galling to the technophiles among us, the market's choice could not be predicted from the technical merits of the contenders. If it could, we'd all have Betamax VCRs in our homes today.

So, DIGITAL decided to have Bill present his results to the SCSI committee at its November 1993 meeting and recommend that the committee extend the SCSI specification to allow the bus to run at up to twice its old maximum clock rate if the components in the physical interconnect met the tighter specifications. Our motive in doing this was purely selfish: we were not ready to choose among the serial bus proposals, yet we would soon need more performance than parallel SCSI could offer. A higher performance parallel SCSI would allow us to improve our storage subsystem performance without having to stake our fortunes on a potential Betamax.

Bill's presentation at the SCSI committee meeting was met with enthusiastic approval. It turned out surprise!—that other system vendors were feeling as uneasy as we were about the serial SCSI buses. The proposal, christened UltraSCSI, was adopted as an extension to the parallel SCSI standard. Bill Ham and the SBTO then worked with component vendors and the SCSI committee to develop the thinner cables, smaller connectors, and SCSI expander circuits described in his paper, all with the aim of keeping parallel SCSI as a desirable alternative to the serial SCSI buses. Today, four years after its committee debut, UltraSCSI is solidly entrenched in the storage market. In fact, storage market analysts are now projecting that the combined volume of devices on all serial SCSI buses (yes, there are still three, but the market has already picked one, Fibre Channel, as the winner) will not exceed parallel SCSI device volumes until early in the next century. And the SCSI committee has finished extending the parallel SCSI specification to achieve a second doubling of maximum bus clock and is in the midst of defining a third doubling.

Without hyperbole it can be said that the technology embodied in Bill Ham's paper has directly affected the course of the computer storage industry, and it continues to affect positively DIGITAL's position in that industry. Enjoy reading the paper and those that follow it in this issue.

Richard Fary

## Recent Advances in Basic Physical Technology for Parallel SCSI: UltraSCSI, Expanders, Interconnect, and Hot Plugging

DIGITAL uses SCSI technology in most of its storage products and consequently has led major standards and industry bodies to improve the technology in the following areas: increased synchronous data phase speed beyond fast SCSI; longer, more complex electrical configurations by means of expander circuits; versatile and more manageable connectivity through a smaller, improved physical interconnect; and dynamic device insertion and removal. Data phase transmission rate extension is achieved through understanding and controlling silicon chip timing and transmission media parameters. Using expander devices to confine transmission line effects to shorter segments allows large increases in the maximum distance between devices and in the device population within the same SCSI domain. Expanders enable complex, hublike configurations to be created without changing existing SCSI devices or software. The use of 0.8-millimeter connector technology and consideration of cable losses has reduced the physical size of the external shielded interconnect by approximately two thirds, decreased the number of parts required to support complex configurations by a factor of 10, and increased the interconnect density to the same level used in serial SCSI. Finally, the mating and demating events that occur during device insertion and removal produce a spectrum of small, undetectable, electrical disturbances on the active bus that appear to be limited by the physics of the media and device capacitance.

#### Introduction

Parallel Small Computer System Interface (SCSI) is the workhorse technology for most of the storage applications in DIGITAL products today. This device and interconnect technology spans all system offerings from the simplest to the most complex. SCSI was introduced to the higher-end products in the early 1990s as the open systems follow-on to the DIGITAL proprietary Digital Storage System Interconnect (DSSI) and Computer Interconnect (CI) technologies.

As system demands have increased, SCSI has evolved to meet the needs. DIGITAL has made considerable contributions to the technology and led the effort to achieve industry standardization. This paper details the most significant developments in the physical features of parallel SCSI technology over the last several years that have allowed it to continue to serve DIGITAL customers in an effective, competitive way. The discussion targets the following four important areas:

- Speed increases in the synchronous data phase, which resulted in the ANSI definition of UltraSCSI (Fast-20 SCSI) technology<sup>1</sup>

- 2. Development of software-invisible circuits, generally called expanders, that enable segmentation of SCSI domains into easily managed pieces

- New connector and cable technology, namely the Very High Density Cabled Interconnect (VHDCI) device, that decreases the interconnect size and complexity by many fold<sup>2</sup>

- 4. Dynamic removal and replacement of devices on an active bus, which is referred to as hot plugging

DIGITAL made substantial contributions in the four areas. This work included creating the expander and interconnect standards projects; leading the working groups that defined the Fast-20, expander, and interconnect standards; providing data for the Fast-20 and hot-plugging projects; and proposing and gaining approval for the hot-plugging standard.

The author has taken a phenomenological approach throughout, because in most cases there are too many unknowns to achieve a rigorous analytical result. This paper focuses on developments from SCSI-2 through UltraSCSI and specifically does not address the new Low Voltage Differential (LVD) technology being introduced for the highest-speed applications.

#### Pedigree

SCSI is defined in several ANSI standards<sup>1,3,4</sup> and in the material that was developed to create these standards.<sup>5,6</sup> The standards were generated over the last decade through a cooperative effort of approximately **6**0 major companies in the computer and computer support industry. As a result of this pedigree, the prime directive for SCSI technology is interoperability of devices designed and manufactured by different companies.

The details of the physical designs used to implement SCSI may not be visible to users and researchers; these details contain much of the marketing and technical differentiation between the products of the participating companies and are therefore hidden in the silicon design. The behavior at the device connector pervades the SCSI specifications. The basic assumption is that as long as the properties are compatible at these connectors, device substitution is possible. Thus, SCSI devices may be both interoperable and of different designs.

#### **Basic Architecture**

This section reviews the basic architecture of parallel SCSI. The SCSI bus is a parallel, multidrop, wired-OR configuration.

**Signal Multiplexing and Phases** The parallel signal construction of the bus allows multiplexing of some signals during different phases of communication so that the same signal lines may have very different functions in different phases. The physical behavior of signals is usually limited by the phase during which the shortest pulses are used and the demands for signal integrity are the highest. The limiting SCSI phase is the data phase (pavload phase) that is executed with the highest synchronous rate. For UltraSCSI, this peak

### Table 1 Terminology for Data Phase Speeds

repetition rate is 20 megahertz (MHz). Table 1 contains the generally accepted terminology related to data phase speeds.

Because of the wired-OR property, each signal in the bus must be driven to a known state even if no SCSI device is actually driving the signal. SCSI uses the logical 0 state (negated state) as the undriven state and uses the bus terminators to drive the signal to this state in the absence of any driving devices. The device signal drivers must overcome this terminator-driven logic state of 0 in order to send a logical 1 (asserted state) onto the signal line.

SCSI signals must support all frequencies, from statically driven by the terminators only (DC) to the third harmonic of the fastest signal edge in the synchronous data phase. In many cases, the same wire must support all these frequencies at different times during the SCSI protocol.

The highest signal edge slew rates for UltraSCSI are approximately 500 millivolts per nanosecond (mV/ns). A 2-volt (V) transition requires approximately 4 ns/5.4 ns/meter (m) = 0.74 m for a signal edge (assuming 5.4 ns/m as the propagation velocity of the signal edge). Therefore, some relief exists because the connectors and cable assembly terminations are much smaller than the signal edge length; the connectors and terminations do not need to have carefully controlled characteristic impedance properties. This allows the use of the technology available in the connector and cable assembly industry to optimize the interconnect properties without the considerable design, manufacturing, and test burden imposed by controlled impedance requirements.

**Transmission Modes** The transmission mode of a SCSI bus is determined by the properties of the terminators that, by definition, constitute the ends of the bus. Terminators also supply most of the energy required to operate the single-ended transmission-mode devices and additionally provide the required matching

| Data Phase Speed Name             | Maximum Transfer<br>Rate (Million<br>transfers/second)' | Maximum Byte<br>Rate (Narrow)<br>(Megabytes/second) | Maximum Byte<br>Rate (Wide)<br>(Megabytes/second) |

|-----------------------------------|---------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------|

| Asynchronous                      | Unspecified                                             | Typically ~ 3                                       | Typically ~ 6                                     |

| Slow (synchronous)                | 5                                                       | 5                                                   | 10                                                |

| Fast (synchronous)                | 10                                                      | 10                                                  | 20                                                |

| Ultra (synchronous) <sup>2</sup>  | 20                                                      | 20                                                  | 40                                                |

| Ultra2 (synchronous) <sup>3</sup> | 40                                                      | 40                                                  | 80                                                |

| Ultra3 (synchronous)⁴             | 80 to 100                                               | 80 to 100                                           | 160 to 200                                        |

<sup>1</sup>One transfer is 1 byte in narrow mode and 2 bytes in wide mode; 1 byte equals 8 data bits plus 1 parity bit. <sup>2</sup>Ultra is synonymous with Ultra1 and Fast-20.

<sup>3</sup>Ultra2 is synonymous with Fast-40.

<sup>4</sup>Rates not yet finalized; Ultra3 is synonymous with Fast-80 or Fast-100.

to the characteristic impedance of the transmission line. In differential SCSI, the terminators provide a small portion of the overall energy required to operate the bus; the differential drivers supply the remainder of the energy.

Drivers that want to transmit an asserted state must overcome the biasing provided by the terminators. The drivers operate locally on the bus and alter the state in their immediate vicinity when they switch on and off. For single-ended SCSI, the 0 state is approximately 2.5 V and the 1 state is approximately 0.5 V. For high-voltage differential SCSI, the 0 state is approximately -1 V to -2 V, and the 1 state is approximately 2 V. (The difference between a state 1 and a state 0 is higher with differential—typically, approximately 4 V.)

For single-ended transmissions, the drivers operate on energy previously stored in the bus by the terminators. This energy is mostly electrostatic energy in the charge stored in the capacitance of the transmission line for negated states and electromagnetic energy in the current flowing through the inductance of the transmission line for asserted states. Ultimately, the terminators will set the state back to negated after the drivers cease to source or sink current; however, this only happens after the round-trip propagation delay from the driver to the farthest terminator if the bus does not have matched characteristic impedance properties.

Approximately the same energy transformations occur for differential SCSI, but significant current is supplied by the drivers for both the asserted and the negated states.

**Multidrop Requirements** The multidrop architecture requires a continuous low-resistance path called the bus path between the terminators and allows devices to be attached to this path. The number and properties of these attached devices vary widely because of many factors including the speed of operation, the overall length of the bus, and the transmission mode. Attached devices always disturb the transmission line properties of the bus path; the key to successful operation is in the management of the magnitude of these disturbances.

Generally, the more capacitance or electrical length the device has, the more disruptive it is. Placing devices too close together along the bus path can cause them to appear electrically as a single super disruptive device. Placing them too far apart can result in an overall bus length that is too long.

**Wired-OR Glitches** During the arbitration phase, when the SCSI devices decide which devices will be sending payload data to or from each other, multiple devices may assert the same control line (BSY) at the same time. Each device that wishes to communicate asserts both the BSY line and its respective device

identification (ID) line. After examining the asserted ID lines to determine which device has the highest ID, all but the device with the highest ID release the BSY line. This leaves only one device, the winner, asserting the BSY line. While the current in the BSY line is readjusting itself from a multiple-driver asserted condition to a single-driver asserted condition, noise pulses (called wired-OR glitches) propagate throughout the length of the signal line and may be detected collectively as an erroneous phase. Therefore, one of the architectural limits for parallel SCSI is the time required for these wired-OR glitches to settle. This bus settle time is set by protocol at 400 ns and must be interpreted as a roundtrip propagation time when using a simple SCSI bus. Allowing some time for propagation through driver and receiver chips yields a maximum physical length for a simple bus of 25 meters.

#### Areas of Improvement

Thus, the opportunities for improving SCSI derive from appropriately managing the transmission lines, taking advantage of the multidrop architecture offered by a parallel wired-**O**R structure, using state-of-the-art technology from the interconnect and silicon industry, and making innovative use of the time required for the wired-OR glitches to settle. These techniques are the basis of the development by DIGITAL in the four areas addressed in this paper.

Speed increases in the synchronous data phase are based primarily on increasing the timing precision in the silicon transceivers by using newer silicon technology. The interconnect properties remain largely unchanged from those used for fast SCSI.

Circuits that enable segmentation of SCSI domains into easily managed pieces are based on systematic isolation of transmission line properties and use of wired-OR noise pulse properties. No software, interconnect, or device changes needed to use these circuits.

New connector and cable technology is based on an innovative 0.8-millimeter (mm) ribbon-style connector technology that optimizes the total SCSI electrical requirements with the capabilities of cable and connector design.

Dynamic removal and replacement of devices on an active bus, i.e., hot plugging, is based on the multidrop architecture, which enables devices to be added or replaced without affecting continuity between other devices. Hot plugging depends on understanding and managing the electrical disturbances created during the insertion or removal.

The remainder of this paper provides details of these four areas of improvement. The end result of these extensions to the basic physical architecture of parallel SCSI is a major increase in its capabilities, accompanied by only a very minor disturbance to the installed base, especially the software.

#### Increasing the Synchronous Data Phase Speed

Beginning with the SCSI-2 standard, the synchronous transmission mode is available for transferring payload data between SCSI devices. The devices select this mode by mutual agreement before any synchronous data is passed. The agreement is achieved by using the asynchronous transmission mode, which is slow but usually reliable.

The synchronous data phase uses the DATA and PARITY bit lines for the data and either the REQ or the ACK control line as a signal that the receiver uses for capturing the data. The term synchronous derives from a specified timing relationship between the bit line signal edges and the REQ or ACK signal edges. (The falling edge of the ACK signal is used when the data phase transmission originates from the SCSI initiator, and the falling edge of the REQ signal is used when the transmission originates from the target.) There is no synchronous relationship between the internal timing references on different SCSI devices, so the receiver must buffer the received data before introducing the data into its internal data management structure. This buffering is usually accomplished by means of a first in first out (FIFO) circuit that uses the REQ or the ACK signal as the latching signal for the incoming data. For convenience, in this paper we only refer to the ACK signal, with the understanding that the same discussion applies to the REQ signal when it is used as the data-latching signal.

Since only the falling edge of the ACK signal is used in the presently specified SCSI versions and an ACK signal is required for every data transfer, it follows that the ACK signal cycles at least twice as fast as the data bits. When a continuous stream of transfers is transmitted, the ACK signal is a regularly repeating signal, nominally, a square wave. An alternating 1/0 pattern produces the highest fundamental frequency for the data bits at half the frequency of the ACK signal. Therefore, the ACK signal requires careful attention since it is the most demanding on the transmission process.

The focus of this section is to examine how the speed of the synchronous data phase was increased by a factor of two to achieve the Fast-20 (UltraSCSI) specification.

#### Status before UltraSCSI

In 1993, the SCSI-2 standard<sup>3</sup> had been in place for two years, and a follow-on standard called SCSI-3 Parallel Interface (SPI)<sup>4</sup> was technically stable. SPI had been created largely because the specifications in the SCSI-2 standard were not effective in implementing the single-ended version of the synchronous transmission (10 megatransfers per second). The differential version specified in SCSI-2 worked well but was much more expensive in cost, power, and space than the single-ended version. Therefore, most of the interest was in making the fast single-ended version work adequately.

Taking single-ended SCSI from asynchronous and slow synchronous (5 megatransfers per second) to the fast synchronous technology was difficult. The prevailing opinion was that the SPI standard represented the final improvement to parallel SCSI. This view set the stage for a number of alternate physical technologies based on the serial point-to-point transmission schemes used in communications technologies, e.g., Fiber Distributed Data Interface (FDDI) and Ethernet, to be used for higher-performance storage applications.

DIGITAL's Storage Bus Technical Office had seen many instances of difficult implementations that were the result of less-than-optimal understanding and management of the specification margins. No credible study had been presented on the margins available in SCSI, so the thrust was to create baseline characteristics of multidrop parallel SCSI to determine where unused margin might exist.

Little data was available on the precise reasons why specific implementations of fast synchronous SCSI did not work. The system would hang or report various error messages with almost no indication of the basic causes. A method that could report margin to failure and mechanism of failure was needed to unravel this situation. Therefore, the approach DIGITAL took was to step back from full SCSI implementations and to examine the pieces without the encumbrance of the SCSI protocol.

One of the most mysterious areas was the behavior of SCSI receivers. The SCSI-2 and SPI specifications used bipolar transistor-transistor logic (TTL) levels as the basic receiver input levels. Almost all SCSI devices were being designed with complementary metal-oxide semiconductor (CMOS) technology, so the differences between the receiver properties presented a key opportunity for hidden margin. Other unknown areas were jitter, cross talk, skew, ground offset, effects of stubs, and worst-case configurations.

DIGITAL built a special test environment to systematically examine each piece of parallel SCSI. The environment was named the PBDIT, an acronym for parallel bus data integrity tester. This test environment made it possible to systematically examine the real margins to failure for the key pieces and to develop the confidence that SCSI could be used at elevated speeds and be made highly robust at the slower speeds.

#### Special Test Environment

The test environment was built to allow known data patterns to be transmitted across a SCSI device, into SCSI transmission media, and then into another SCSI device. The same data pattern is loaded into both sides so the receiver knows exactly what data it is supposed to receive. The transmitting side is called the exciter, and the receiving side is called the comparator. Received data is committed to the comparator by using one bit line as the latching ACK signal in a manner exactly like that specified in synchronous SCSI transmissions. The test environment allows the position of the ACK signal to be adjusted with respect to the data signal edges.

Since the comparator knows the data pattern that is transmitted, it is possible to isolate the precise data bit that caused the transmission error. This kind of errordirected methodology has found widespread use in the integrated circuit industry.

Other features of this test environment include detachable load boards that contain the SCSI drivers, terminators, receivers, connectors, or any other physical media-dependent components. The minimum requirements for a load board are that the exciter contain the SCSI driver and a connector and that the comparator contain the SCSI receiver and a connector. Other components may be placed between the load boards for different test conditions. The SCSI driver must have accessible points for the exciter logic, and similarly, the SCSI receiver must have output points to drive the comparator. These requirements eliminate drivers and receivers that are imbedded within chips with other functions. Fortunately, separate SCSI drivers are available for both single-ended and differential versions. (The differential versions normally use separate chips, but only a few choices are presently available for the separate single-ended versions.)

The test environment is useful for developing the understanding of operating mechanisms and for measuring the margins for specific hardware configurations. This environment is not useful for deriving specifications, since the performance at the specified interfaces, i.e., the device connectors, is not directly observable. Oscilloscope measurements provide the basis for setting compliance specifications, since these measurements can be performed at the connectors. The basic question that needed an answer was, Can parallel SCSI be operated at elevated speeds with reasonable margin to failure? DIGITAL optimized the special test environment to answer this question. Other specifications that would be necessary to ensure interoperable operation between UltraSCSI devices could be derived if it appeared possible to achieve the end result.

The data pattern loading and digital control of the exciter and the comparator were achieved through optically coupled means. This allowed the ground offset voltage to be adjusted between the driver and the receiver without compromising the operation of the logic.

The data flows only from the exciter to the comparator. If bidirectional information is desired, the physical connections between the exciter and comparator have to be reversed. This scheme leaves untested the cross-talk effects on the REQ signal that is traveling in the opposite direction to the ACK signal (if ACK is synchronized with the data as in a write operation). Separate measurements are necessary to examine this issue. Cross talk into other control lines is addressed by holding these lines constant in the data pattern transmitted.

The SCSI standard deals with the REQ cross-talk issue by requiring that the data lines be physically separated from the REQ and ACK lines in the transmission media. Measurements not reported in this paper have confirmed negligible speed-related cross talk into the REQ line.

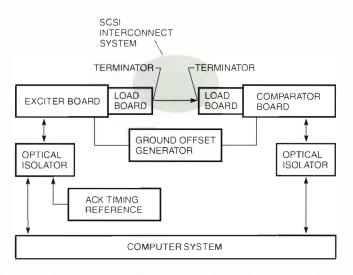

Up to 27 pairs of 3-byte-wide lines (wide SCSI uses only 18 pairs for high-speed transmissions) can be tested with the special test environment. Figure 1 is a functional diagram of the test environment. The SCSI terminators are shown as separate from the load

**Figure 1** Special Test Environment

boards in this case. A key feature of this kind of testing is that the test does not necessarily stop when an error is detected. In fact, the environment may detect errors 100 percent of the time. This acceptable behavior allows mapping of the complete bit-error response of the system.

**Sample Data from the Special Test Environment** The test environment allows a multitude of tests to be performed. The test scheme described in this section is the one that was used to establish the basic timing margins available from normal SCSI silicon, cables, connectors, and terminators.

A random repeating data pattern with 16 thousand different bit combinations was used as the basic data pattern. This pattern was transmitted over a period of time, and the number of errors detected was recorded. In this test, an error is defined as one or more bits in the received data transfer that do not match the transmitted bit. To acquire a new error rate data point, the transmission test is repeated by using exactly the same number of transfers in the same time period with the same data pattern but with some test parameter changed.

Virtually any parameter can be varied for different tests. For a given physical configuration, the most useful parameter for determining the timing margin is the position of the ACK pulse with respect to the data edges. The basic data then becomes the number of errors detected and the position of the ACK pulse edge.

There are two basic random variables operating in this scheme: the data pattern and the jitter induced by non-data-dependent sources. It is easy to separate these two variables by using extremes in the data pattern: very few transitions and the maximum number of transitions (every data edge has a transition, i.e., alternating 1/0 pattern). Although this level of precision is available, we will see that we really do not need to bother for parallel SCSI at the maximum UltraSCSI rate.

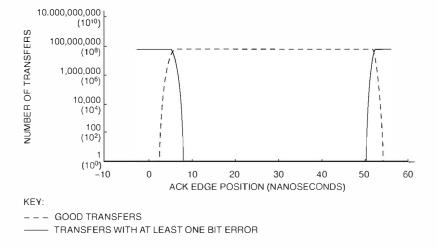

Figure 2 shows a typical error rate plot from a simple single-ended configuration made from ordinary SCSI interconnect hardware and transceivers being tested at the maximum UltraSCSI rate. Each data point represents a 3-second sample (60 million transfers) at each ACK position. The ACK position is incremented in 0.1-ns steps for a total of 240 independent tests in the plot. To minimize the testing time, we tested only the time ranges from -3 to 9 ns and 44 to 56 ns. The individual data points are not distinguishable in this presentation, and there is very little scatter between neighboring points. In Figure 2, the error rate of 1 is used to indicate that no errors were detected, since the log of 0 is not easy to plot.

Examination of the raw data reveals that the plot is monotonic in detected error rate to the fourth decimal place. This indicates an extremely predictable situation as far as behavior of the same set of hardware is concerned. That is, there is virtually no Gaussian jitter present, and a SCSI system could be designed to be quite reliable and stable at the maximum UltraSCSI rate.

Extending the sample period to 5 minutes made no difference in the position of the key features. Using the 3-second sampling time, the entire data set could be acquired automatically in approximately 12 minutes.

The onset of errors is extremely sharp as the ACK position approaches the critical position. One hundred picoseconds changes the observation from 0 to 864 errors near the 8-ns position. On the other end, the 50.1-ns time produced 7 errors, and the 50.2-ns time produced 425 errors. No errors were detected at any of the times between 50.1 ns and 7.9 ns. This data shows that there are no strange effects that prevent SCSI from operating at the maximum UltraSCSI rate.

As the ACK position proceeds into the region of more errors, a condition is finally reached in which *all* the transfers have errors. On the one hand, the probability that one transfer has the same data content as its

Figure 2 Typical UltraSCSI Error Rate Plot

neighbor's is very small with this random data pattern. On the other hand, since a random data pattern is being used, there is a reasonable chance that a bit will actually match that transmitted in one state but not in the other state. The random data pattern tends to spread out the time between the first error and the last good transfer. In the limit, for perfectly random data, this time is a measure of the total timing imprecision in the system.

This imprecision includes skew in the exciter and comparator boards, in the SCSI drivers and receivers, and in the cable transmission media (including loads, if any), and all forms of jitter. For the test conditions shown in Figure 2, the total difference is 3.6 ns near the 5-ns point and 5.4 ns near the 52-ns point. This shows that the skew specifications in the SCSI standard are overspecified as compared to actual hardware performance.

The data shown in Figure 2 is representative of a large variety of configurations up to approximately 3 meters long and loaded or up to much longer pointto-point lengths (20 meters or more [see Figure 6]). The error-free window can be made to collapse by adding too many loads or by using the wrong impedance cable, improper terminators, receivers with the wrong threshold voltages, or other bus component and configuration parameters. However, the details of the actual hardware and configuration do not affect the basic conclusion derived from Figure 2, namely, that a great deal of timing margin is available at the maximum UltraSCSI rate when ordinary SCSI hardware is used.

To put this into perspective, basic gigabit-per-second serial transmissions with approximately twice the basic bandwidth of UltraSCSI have bit times of about 1 ns and timing margins of a few hundred picoseconds. UltraSCSI has an effective margin window of a few tens of nanoseconds. This represents two orders of magnitude more margin for the parallel SCSI application. The initial errors usually originate from the same bit. This bit is the one with the most unfavorable timing skew with respect to the ACK signal. The cliff is not perfectly sharp because there is a 50 percent chance that the data transmitted is the same as that expected even under the error case and, more importantly, because there is some level of jitter present. It is this jitter that softens the cliff. Thus, the first errors detected happen when the skew of the weakest bit adds to the tail of the jitter distribution. Only a few errors are present because only a small part of the jitter population extends far enough to trigger the error. SCSI systems will experience virtually no errors because of these mechanisms in service if one operates 1 ns or more away from an error cliff.

Note that these results from the special test environment almost always yield margins higher than those calculated from a set of interoperability specifications. This is because the interoperability specifications must allow margin for each piece, and the special test environment reports the integrated result from many pieces in the complete SCSI connection.

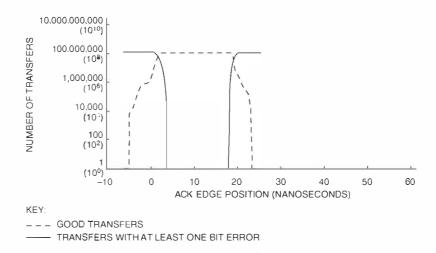

**Higher Speeds** The main effect of further increasing the transfer rate above the maximum UltraSCSI rate in the same set of hardware is to change the time position of the onset of nonzero error rates and to narrow the error-free region. Figure 3 shows an example of data from Fast-40 transmissions using separate highvoltage differential transceivers on each bit. (This data was acquired by DIGITAL's Storage Bus Technical Office in 1994.)

The error-free zone has narrowed to approximately 15 ns, and the time between first error and 100 percent errors has widened on both sides, but still no uncontrolled regions exist. This strongly suggests that at least Fast-40 transfer is possible with no major technology changes in the interconnect.

#### Figure 3 Fast-40 Error Rate Plot

12

Digital Technical Journal

Additional Tests Other tests that are useful with the special test environment are ground offset effects, terminator power effects, correlation of time domain plots on the signals with error rate distributions, hotplugging testing (which results in good error detection), and comparison of the impact of different cables and transceivers. Test results of this nature are not included in this paper because the impact of these variations depends on many parameters and the results may not be generally applicable.

#### Timing Specification Methodology

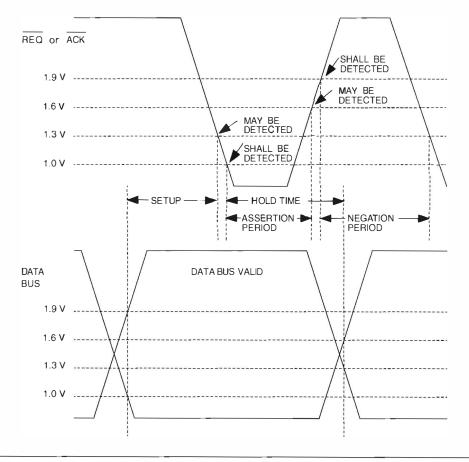

With the increased emphasis on timing precision for UltraSCSI technology, it was necessary to introduce better specifications for the measurement of timing parameters than those in the SCSI-2 and SPI standards. Figure 4 shows the precise measurement points and features used for the specification of single-ended UltraSCSI signals.

The effects of the finite slew rate on the signal edges are accounted for largely by specifying the voltage levels that coincide with the receiver input levels. Thus, the setup time ends when the receiver is able to detect an asserted state at 1.3 V, and the asserted period begins when the asserted state has been detected. On the negation side, the signal must rise to at least 1.6 V before the receiver can detect a negated state, and a negated state must be detected if the input signal reaches 1.9 V. In the SCSI-2 and SPI standards, any point between 0.8 V and 2.0 V could be used as the timing measurement.

#### Sample UltraSCSI Signals

Numerous variations on the details of the signals can be produced in UltraSCSI configurations. This section shows two types of signals as representative examples that validate UltraSCSI as viable under certain conditions. The first case explores a configuration that actually exceeds the recommended specifications. This is a complex cabled environment with a cluster of loads on one end and some distributed loads on the other end. The second case shows the signals over a 25-meter, single-ended point-to-point bus.

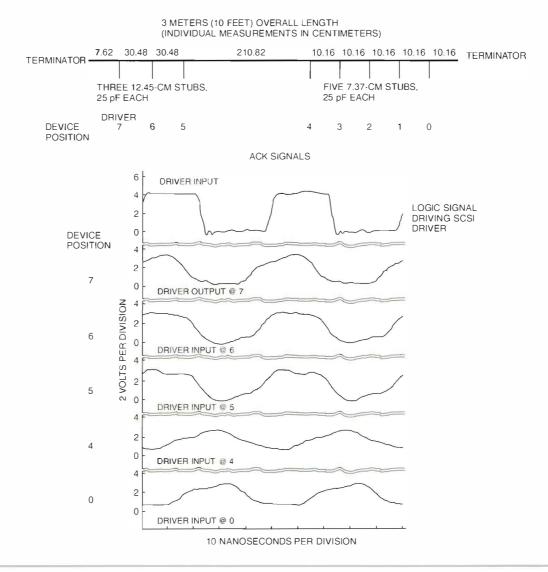

**Complex Loads** Figure 5 specifies a complex configuration and the single-ended SCSI signals that result at various positions along the bus. The logic

signal that is driving the SCSI driver chip is the first trace at the top; it provides a common timing reference for all the signals. The weakest signal is at device position 4, just after a relatively long run with no loads. This signal is below the 1-V level but has a very slow assertion slew rate that causes considerable loss of asserted state pulse width. This complex configuration works with the receivers used but does not have the timing margin required by the Fast-20 standard.

By varying the position of the loads so that there are no loads between the driver and the first load (not shown), the signal at the first load device is degraded even more than at position 4 in Figure 5. This is one reason that the overall length of single-ended UltraSCSI with many loads is restricted to 1.5 meters and that the total number of loads is limited to 8.<sup>4</sup> UltraSCSI devices connected to backplanes may be especially sensitive to attached cables that extend the total bus length more than 6 to 8 centimeters (cm) beyond the backplane. This reduced bus length is rather severe when compared to that allowed at the maximum fast SCSI transfer rate (a total of 3 meters).<sup>4</sup> In the section Small, Improved Interconnect, we show how to overcome this 1.5-meter, 8-device limit by using an active SCSI interconnect.

Applying the timing measurement methods shown in Figure 4 to the waveforms in Figure 5 illustrates that more careful timing specification methods do indeed help significantly to keep the timing margin high enough to use.

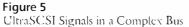

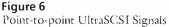

**Point-to-point Configuration** If loads are present only at the ends of the bus, the transmission line between SCSI devices improves electrically. This occurs simply because the loads significantly disrupt the characteristic impedance and cause reflections and attenuation. The point-to-point signal at 25 meters has better amplitude and timing margins than signals in much shorter buses with closely spaced loads. Figure 6 shows a typical example of a point-to-point UltraSCSI signal. The format used in Figure 6 is the same format used in Figure 5.

#### Differential UltraSCSI

Differential UltraSCSI uses the same configuration rules as fast SCSI (25-meter total length, 20-cm [8-inch] stubs, 16-device load)<sup>1</sup> and uses the same timing values as single-ended UltraSCSI. The larger signal amplitudes and the common mode rejection property of differential transmissions help overcome the transmission line weaknesses in heavily loaded and long buses. As with any high-voltage differential system the costs—in terms of money, power, and space—are higher.

#### Other Requirements for UltraSCSI

The Fast-20 standard<sup>1</sup> contains a number of detailed requirements on the components used in UltraSCSI configurations. Included are slight modifications to the cable impedance, active negation requirements for drivers, special length limits for certain loading conditions, restrictions regarding the kinds of single-ended terminators to use, and timing budgets.

#### Summary of Developments in the Area of Increased Synchronous Data Phase Speed

The UltraSCSI (Fast-20) speed increase can be attributed to a systematic examination of the margins present in actual SCSI hardware and to the elimination of the excess margins. Advances in the integrated circuit industry enabled silicon designs to be specified with tighter controls on the driver and receiver timing and threshold properties than were possible when the SCSI-2 or SPI standards were developed. All the important changes needed for SCSI devices are contained in the silicon designs for the drivers and receivers. As a result, the user sees no difference between the appearance of UltraSCSI and that of ordinary SCSI.

The system integrator must use a more restrictive set of configuration rules than required for fast and slow SCSI. Also, the only impact on software is the addition of a new speed agreement code for the rates uniquely supported by UltraSCSI. This negotiation is done precisely the same way for UltraSCSI as for any other form of SCSI. Finally, UltraSCSI devices are 100 percent backward compatible with fast and slow devices. Although a device may be capable of the maximum UltraSCSI rate, it may be needed in a configuration that does not support UltraSCSI. In such a case, the UltraSCSI device would be used in the fast or slow mode and would have more margin at those slower speeds than it would if it were not UltraSCSI capable.

#### **Bus Expanders**

As noted previously in the discussion of complex loads, there are rather severe limits on the configurations that can be achieved with single-ended UltraSCSI when implemented in a single bus. The extension to parallel SCSI architecture that overcomes this constraint involves using active circuits that connect SCSI buses electrically but isolating them from each other in a transmission line sense. These circuits have the general name expanders, since they expand the configuration capabilities of parallel SCSI.

Each individual bus has two terminators and its own transmission mode (single ended or differential) and obeys transmission line-based configuration rules as if it were the only bus in the system. When used with expanders, these individual buses are called bus segments. The collection of SCSI devices in all the bus segments that are electrically connected together is called the SCSI domain. One example of a SCSI domain using expanders is shown in Figure 7. Note that when using expanders, it is possible to have bus segments that do not have any SCSI initiators or targets but only serve to form an electrical interconnect between other bus segments.

#### **Expander Properties**

Expanders are available in two basic types: simple and bridging. Bridging expanders behave as a SCSI initiator or target, whereas simple expanders have a set of properties that make them look like a piece of wire with delay to the protocol. Simple expanders

- Cannot initiate SCSI IDs and arbitrations and cannot originate messages, although the expanders can read messages sent from initiators and targets

- Allow minimal arbitration propagation delay

- Yield a retransmitted signal timing skew (both delay and high/low) no worse than from valid SCSI initiators or targets

- Do not interfere with the REQ/ACK offset count

- Allow min/max pulse widths to be maintained

- Require the filtering of the SCSI RESET line

- Allow arbitrary placement of the initiator and the targets

- Require that terminator power not be connected between the segments being coupled

- Do not need to know the negotiated data phase speed or any other variable property of a transaction

- Require that there be no electrical or logical connection of the DIFFSENS line (a single-ended signal that indicates the transmission mode being used on the bus segment) between segments being coupled

- Issue a SCSI bus RESET signal on one segment on detecting transmission mode (single-ended/LVD, etc.) changes on the other segment

Simple expanders are becoming available from several sources in the industry for use with UltraSCSI.

#### Domain Rules Using Simple Expanders

When using only simple expanders in a domain, six rules must be observed:

- 1. All bus segments in the domain must comply with their individual bus segment length limits and other segment-related requirements.

- 2. Any segment between two other segments must support the highest performance level that can be negotiated between the two other segments. For example, two wide UltraSCSI segments must not be separated by a segment that does not support both wide SCSI and UltraSCSI.

- 3. The maximum propagation delay between any two devices in the domain cannot exceed 400 ns. A special case exists for devices that use extremely long times for responding to BUS FREE (the so-called BUS SET DELAY)—the one-way propagation limit is 300 ns instead of 400 ns.

- 4. The number of addressable devices cannot exceed 16 unless the domain contains bridging expanders.

- 5. A branch/leaf architecture must be observed; loops are not allowed.

- 6. The REQ/ACK offset negotiated between any two devices must be large enough to ensure that adequate offset and buffering is available to accommodate the round-trip time between the devices. For the maximum UltraSCSI rate with a 400 ns maximum one-way domain propagation time, the

#### Figure 7 SCSI Domain Built Using Expanders

minimum offset is 18. (This offset level is derived by considering a maximum round-trip time of 800 ns at 50 ns per transfer [800/50 = 16] and somewhat arbitrarily adding two transfers to account for some additional delay due to the processing time in the silicon.)

Achieving the 400-ns one-way domain delay requires expanders that will not pass the wired-OR glitch (noted earlier in the introduction) between bus segments. This filtering of the glitch allows the bus segments to settle individually.

The propagation delay through an expander directly subtracts from the physical distance between devices. It is therefore desirable to use expanders with small delays. For a single-ended-to-single-ended application, the delay can be as low as 10 ns. For a single-ended-to-differential application, the delay is typically around 100 ns, which is another significant penalty to using differential bus segments.

More detail concerning these rules and other properties is available in the draft ANSI document: *SCSI Enhanced Parallel Interface*,<sup>5</sup> which was edited by the author of this paper.

#### Summary of Improvements Related to Bus Expanders

The use of simple expanders dramatically extends the utility of single-ended UltraSCSI. The most obvious example is the ability to introduce point-to-point segments where additional length is needed. A less obvious example is the ability to create star or hub configurations by clustering simple expanders into a local physical area. An example of a three-port SCSI hub is shown in Figure 7. Note the three simple expander circuits internally connected within the hub. Simple expanders also make it possible to mix single-ended and differential SCSI devices in the same domain, to achieve the full 16-device count, to add and remove bus segments without shutting down the entire domain, and to achieve differential performance without incurring the extra cost of differential. Bridging expanders offer the same transmission isolation as simple expanders and may allow increasing the number of devices in the domain to as high as 946,5 but bridging expanders are not as well developed as simple expanders and will not be explored in depth in this paper.

Note that the improvement in signal integrity is dramatic when using expanders with backplane applications. Therefore, it is good practice to use an expander whenever connecting a SCSI cable to a backplane that contains SCSI devices.

#### Smaller, Improved Interconnect

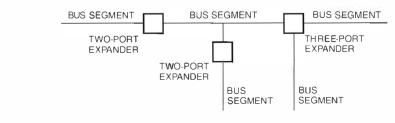

Another recent development in parallel SCSI technology is the introduction of much smaller external physical interconnects and more capable internal device interconnects. The SCSI connectors and shielded cables have historically been large, bulky, and generally difficult to manage.

Spearheaded by activities that began in 1995 in the SFF (formerly Small Form Factor) industry group, standardization is under way of two new connector families that offer unprecedented levels of functionality and true multisourcing of complete connectors for parallel SCSI. These families are the Very High Density Cabled Interconnect (VHDCI)<sup>2</sup> shielded connectors that reduce the overall size of an external connector by two thirds and the Single Connector Attachment–2 (SCA-2)<sup>7</sup> unshielded connectors that integrate into a single connector all the functions needed to run a peripheral. The VHDCI family revolutionizes the external SCSI interconnect; the SCA-2 family does the same for the internal device interface.

For the first time, complete connectors-not just the mating interface-are being standardized. This feature is essential to achieving interchangeability and second sourcing for connectors with the same style of termination-side contact. The VHDCI family is specified in 26 different forms, all with exactly the same mating interface, so that virtually any kind of device or cable assembly design can be accommodated. Interestingly, this array of choices for the connectors does not increase the complexity of the interconnect but rather opens up new ways for product developers to design products while maintaining a simple and physically interoperable separable connector interface. In fact, this ability to accommodate a variety of product design requirements without changing the separable interface is one reason that SCSI is becoming less complicated.

Similarly, the family of SCA-2 connectors for SCSI internal devices and cables is following the VHDCI standardization model, with a significant number of intermatable forms being standardized. These connectors offer the ability to bring all the SCSI signals, all the power and ground connections, and all the optional signals, such as IDs, spindle sync, and power fail, out of the device through a single unshielded connector. This feature dramatically shrinks the cost and complexity of interconnecting an array of SCSI devices.

Using an SCA-2 connector, the device may be inserted into a backplane without using cables. If the SCA-2 and backplane combination is not used, a SCSI cable (50-pin or 68-pin conductor), a four-lead power cable for ground and power (5-V and 12-V), and one or more smaller cables for the IDs etc., are required for *every* device in the system. Each of these cables is routed differently, has different current carrying and other electrical requirements, and has very different connectors. Although this cabled option is flexible and offers significant advantages in some systems, it is usually not the best solution in the device array and modular packaging applications that are required for the higher-end applications. Therefore, the SCA-2 is a significant factor in the dramatic reduction in complexity of higher-end SCSI device applications.

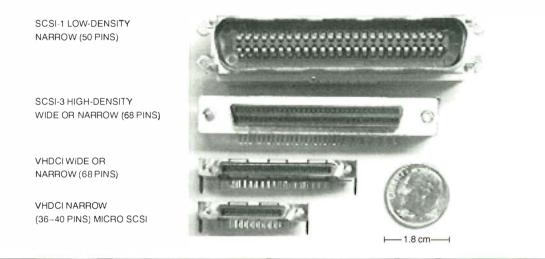

#### VHDCI Connectors

The physical size of the VHDCI connectors is much smaller than the earlier versions, as seen in Figure 8. Because of its low profile, the VHDCI 68-pin family is approximately half the height and twice the width of the latest Fibre Channel external connector, the High-Speed Serial Data Connector (HSSDC). Figure 9 shows a comparison of the VHDCI and HSSDC connectors. The same panel space is required for either technology.

The VHDCI connectors shown in Figure 9 are closely spaced, but the orientation of the polarizing shield connection is 180 degrees different between the upper and lower connectors. This arrangement allows an offset cable assembly to be used where one side is flat. This same cable assembly may be used on both the upper and lower connectors without interference. The specifications of the VHDCI interface ensure that neighboring PC option slots will not have interference even if all the SCSI ports have cable assemblies attached.

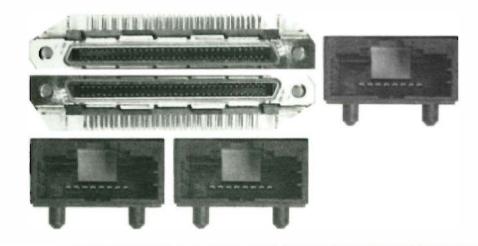

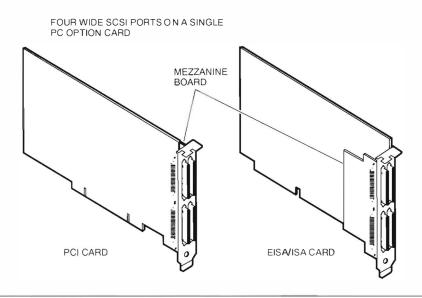

The VHDCI connector is useful for multiport applications such as RAID (redundant array of inexpensive disks) controllers. Figure 10 shows examples in which the wide version of the connector family has allowed at least a doubling of the number of ports possible in a single controller form factor. As illustrated in Figure 10, the device design enables up to four wide SCSI ports on a single PC option card cutout.

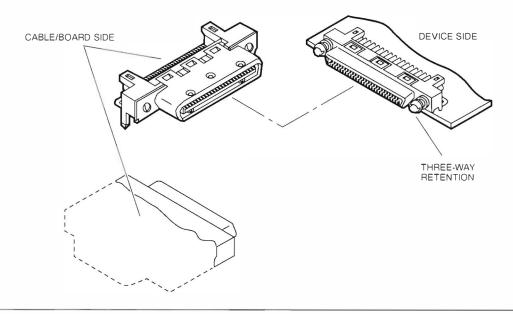

The VHDCI retention scheme is also significantly simplified by introducing a three-way retention post for the bulkhead connector. This post accepts (1) the conventional jackscrews, (2) a squeeze-to-release clip for positive retention with rapid release, or (3) a detent ring retention that requires a stronger pull than that required with no retention but no action other than

Figure 8 External SCSI Connectors

#### Figure 9

Comparison of the 68-Pin VHDCI and Fibre Channel HSSDC Connectors

#### Figure 10

Four Wide SCSI Ports on a Single PC Option Card

pulling or pushing. The choice of retention type is made in the cable assembly. All 68-pin VHDCI cable assemblies that comply with the SFF specifications work on all 68-pin VHDCI mating connectors.

Figure 11 shows the details of the 68-pin VHDCI system. The lip in the jack post provides the securing point for squeeze-to-release clips and for split-ring detent retention. The center of the jack post is threaded for use with jackscrews.

Although smaller than the high-density connector, the VHDCI connector is durable. It has no pins that can bend; its retention scheme uses the same-size jackscrew thread as the high-density wide connector; and its contacts are imbedded in the housing where they cannot move or become distorted.

#### SCA-2 Connectors

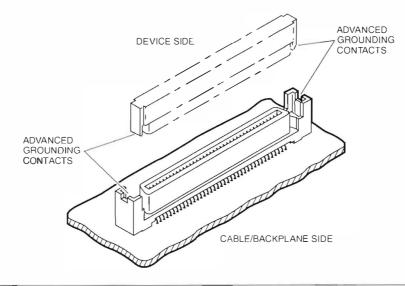

The SCA family uses an 80-position, leaf-style contact to interface all active SCSI lines, three power voltages, and device control signals. This connector is considerably smaller than the collection of the three different connectors used for power, options, and SCSI bus in a cabled system. There are two basic versions of SCA connectors: SCA-1 and SCA-2. Both versions are unshielded and useful only within shielded enclosures. The SCA-1 has 80 positions with all contacts designed

Figure 11 Overall View of the 68-pin VHDCI System

to be the same length. The SCA-2 can be mated to the SCA-1 but has advanced grounding contacts and sequenced signal and power contacts for supporting hot plugging and blind mating (no visual feedback during mating). Both versions are available in many styles, which differ by the termination-side structure and overall orientations.

The SCA-1 is not a documented standard and is being replaced by the SCA-2. The SCA-2 connector was introduced to SFF in 1995<sup>7</sup> as the first step toward formal standardization.

Two special features exist in the SCA-2 connector. First, two contacts, one on each side of the connector, provide the first make/last break for the ground connection. This design ensures that a common electrical ground is established between the device and the system before any power or signal connections are made on device insertion. Upon removal, these contacts ensure that the ground stays intact throughout the disengagement of the signal and power pins.

The second feature allows the special long power contacts to precharge bypass capacitors before the main power contacts make. This reduces the disturbance to the power distribution system and eliminates any arcing on the service power pins. Two pins at the extreme ends of the connector indicate that the connector is fully mated. The overall view of the SCA-2 system is shown in Figure 12.

The size of the connectors in the SCA family has not decreased dramatically. The connectors need to maintain enough size to achieve blind mating alignment, and, for backplane applications, there is little advantage in having a connector that is smaller than the device. With 89-mm (3.5-inch [in]) or the newly proposed 76-mm (3-in) form factor devices, the SCA connector comfortably fits within the device boundaries. The use of backplanes for direct device attachment is possible because all the electrical connections for the device are available in one connector on the device. This design eliminates the cables used to attach the device and the space required for the connectors, thus significantly shrinking the size required to package multiple devices.

#### External SCSI Cable

The external cable for SCSI is shrinking also, through the use of smaller-gauge wire, better dielectrics, and less jacketing material, as illustrated in Figure 13. Formerly, wide SCSI required a cable of approximately 12.70 mm (0.50 in) in diameter (a 126.677-mm<sup>2</sup> [0.196-in<sup>2</sup>] cross section) with 28-gauge wire. Today, wide SCSI cables with 30-gauge wire are shipping with diameters of 9.40 mm (0.37 in) (69.398-mm<sup>2</sup> [0.107-in<sup>2</sup>] cross sections). Cables with 7.62-mm (0.30-in) diameters  $(45.61-mm^2 [0.07-in^2]$  cross sections) are possible with 32-gauge wire and inexpensive dielectrics for wide SCSI. Cables with 6.35-mm (0.25-in) diameters (4.987-mm<sup>2</sup> [0.049-in<sup>2</sup>] cross sections) for narrow SCSI (45.61-mm<sup>2</sup> [0.07-in<sup>2</sup>] cross sections) are flexible and manageable-similar in size and flexibility to a desktop computer power cord and smaller than many serial cables. When used with active single-ended, LVD, or HVD terminators, the 32-gauge wire is adequate for distributing terminator power and SCSI signals in most applications. Long cables should not be used for terminator power distribution.

Further reductions in the connector and cable sizes need to be weighed against the ease of handling, the need for sufficient strength to survive normal service stresses, and the cost increases at very small sizes. The combination of the VHDCI connector and 30/32-gauge wire sizes is a good optimization.

Figure 12 Overall View of the SCA-2 Connector System

Figure 13 External SCSI Cable Diameters

#### Summary of the Benefits Derived from a Smaller, Improved Interconnect

The VHDCI connector and smaller cables combine to offer a robust yet user-friendly revolution in SCSI interconnect. The leaf-style contact of the SCA connector eliminates problems with bent pins that frequently bedevil the older wide SCSI connector. The ability to use up to four wide UltraSCSI ports in a single PCI option slot increases the SCSI connectivity per PCI slot to 60 devices (from 15 devices). By using multiple PCI slots, hundreds of SCSI devices can be connected to a single PC or workstation. In addition, the SCA-2 connector implements the essential contact sequencing required to perform SCSI device hot plugging.

#### **Device Insertion and Removal Bus Transients**

The multidrop feature of the SCSI bus allows device removal and replacement without disturbing the communications between other SCSI devices, if the electrical disturbances caused by the device being added or removed are not detected by any other SCSI devices. Thus, it is architecturally possible to dynamically reconfigure the device population without interrupting existing data transmission processes between operational devices.

The transients involved with device insertion and removal include mechanical vibrations, power distribution instabilities, SCSI terminator power noise, electrostatic discharge (radiation and induced current), and SCSI signal line noise. All except the SCSI signal line noise and the terminator power noise are handled by the storage system design and therefore are not directly part of the advancements in parallel SCSI. The SCSI terminator power noise is determined by the size of the decoupling used on the SCSI terminators and the size of the capacitance on the device being inserted. This noise is easily controlled by ensuring that these sizes meet the values specified in the SPI standard.<sup>4</sup>

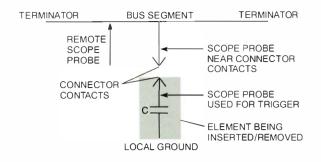

The delicate case is when the SCSI signal lines arc involved, which is the subject of this section. To determine the nature and magnitude of these signal line disturbances, one must understand the following three mechanisms: (1) the overall sequence of events, (2) the electrical dynamics of connector contacts when used in the SCSI application, and (3) the electrical consequences on the bus when the device makes/ breaks contact with the SCSI signal line.

There are two sequences of interest: insertion and removal. The removal process is easy to grasp after the insertion process is understood.

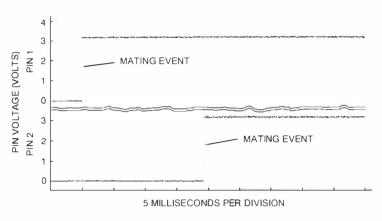

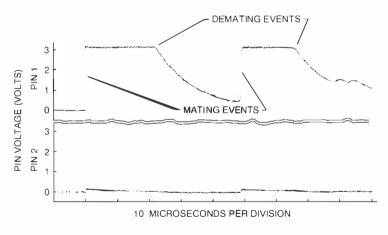

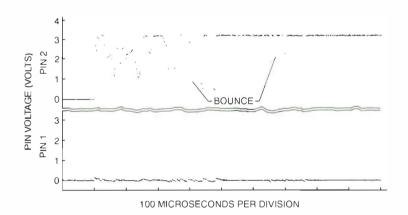

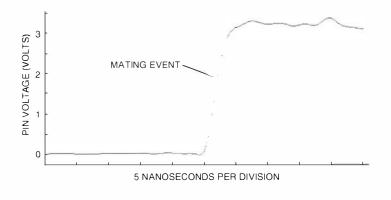

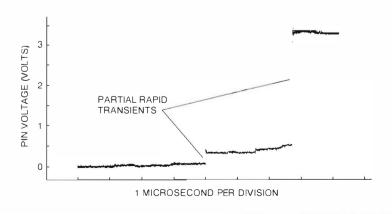

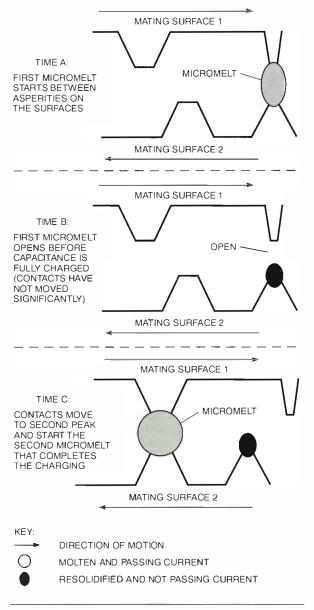

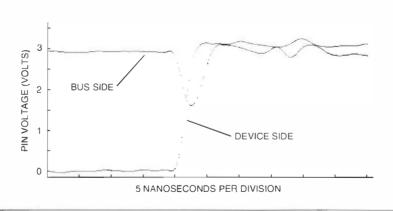

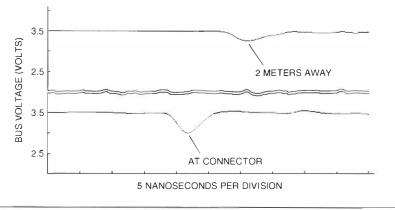

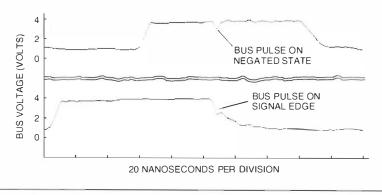

#### Single-ended Device Insertion